5 DERECHA

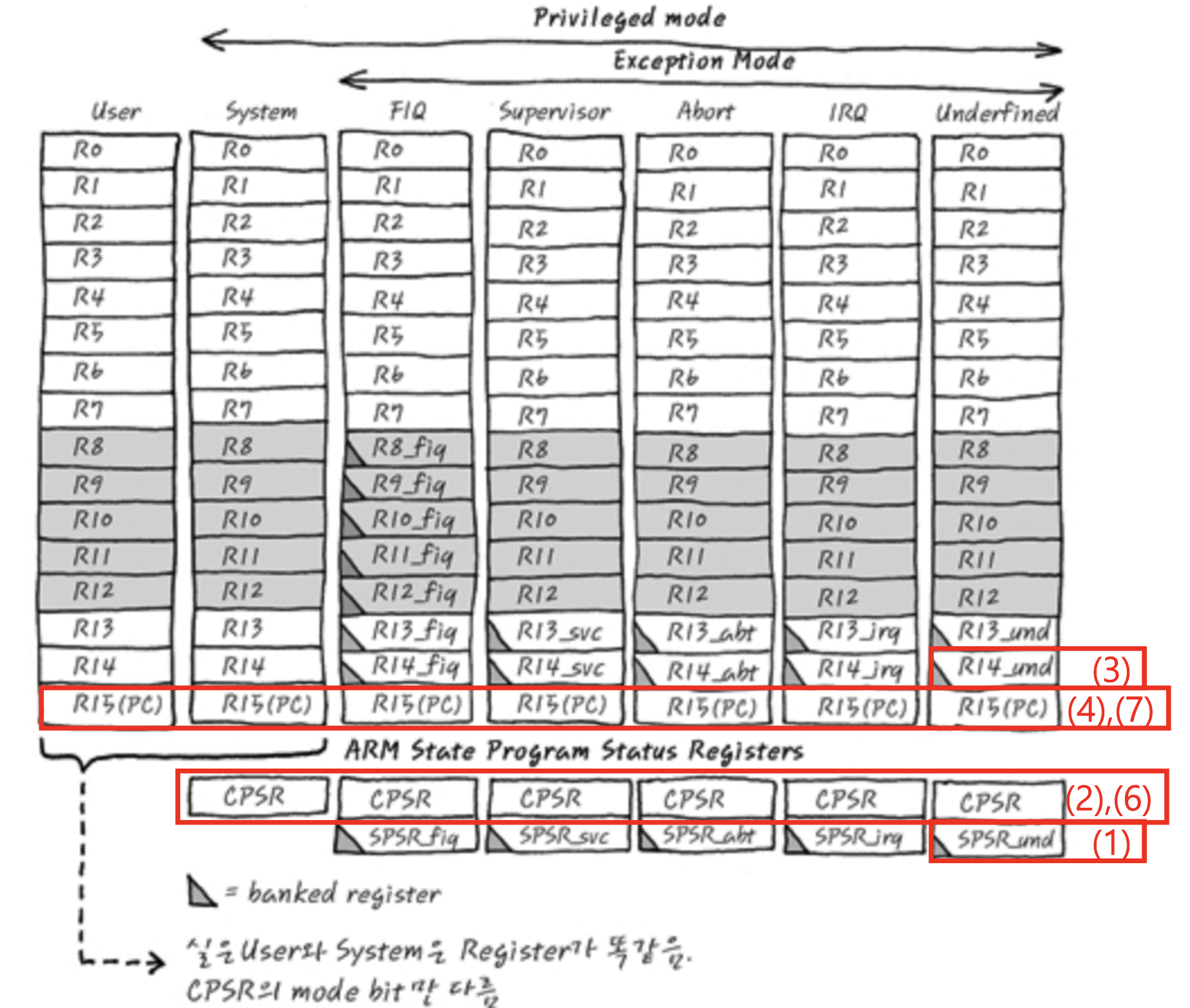

ARM Mode & Register 본문

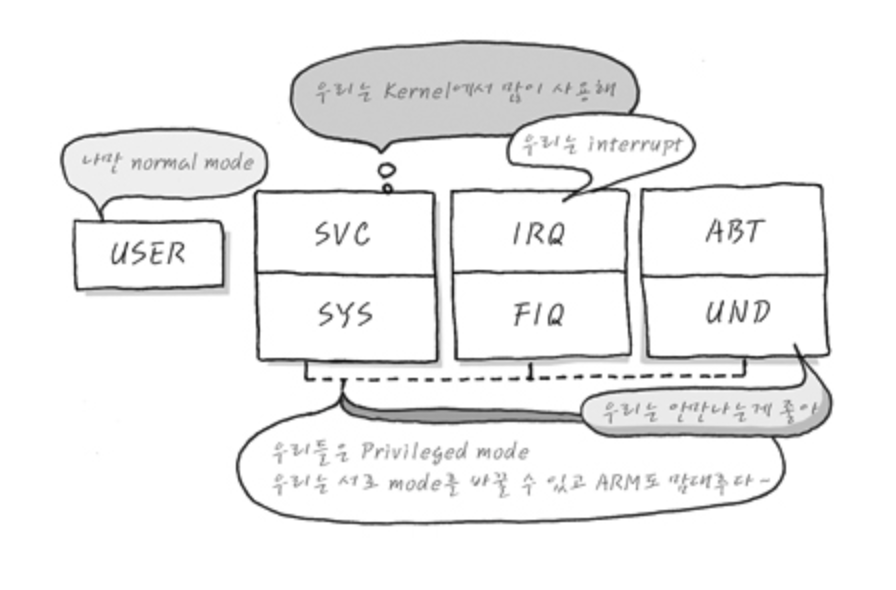

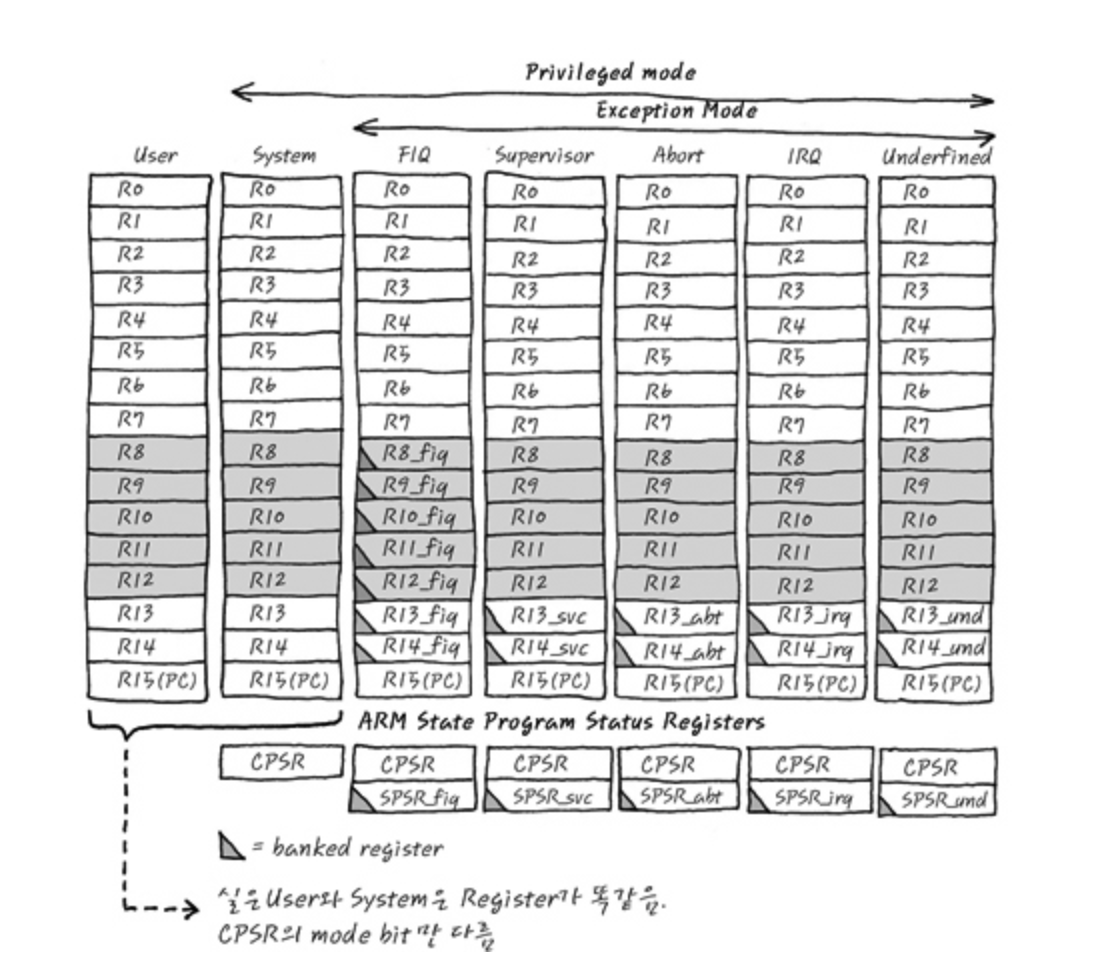

(1) ARM Mode

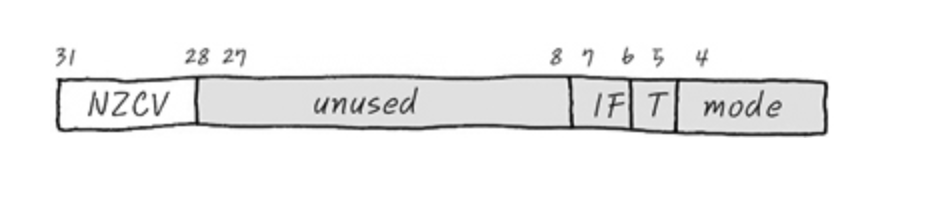

(2) Bit

(3) mode Change

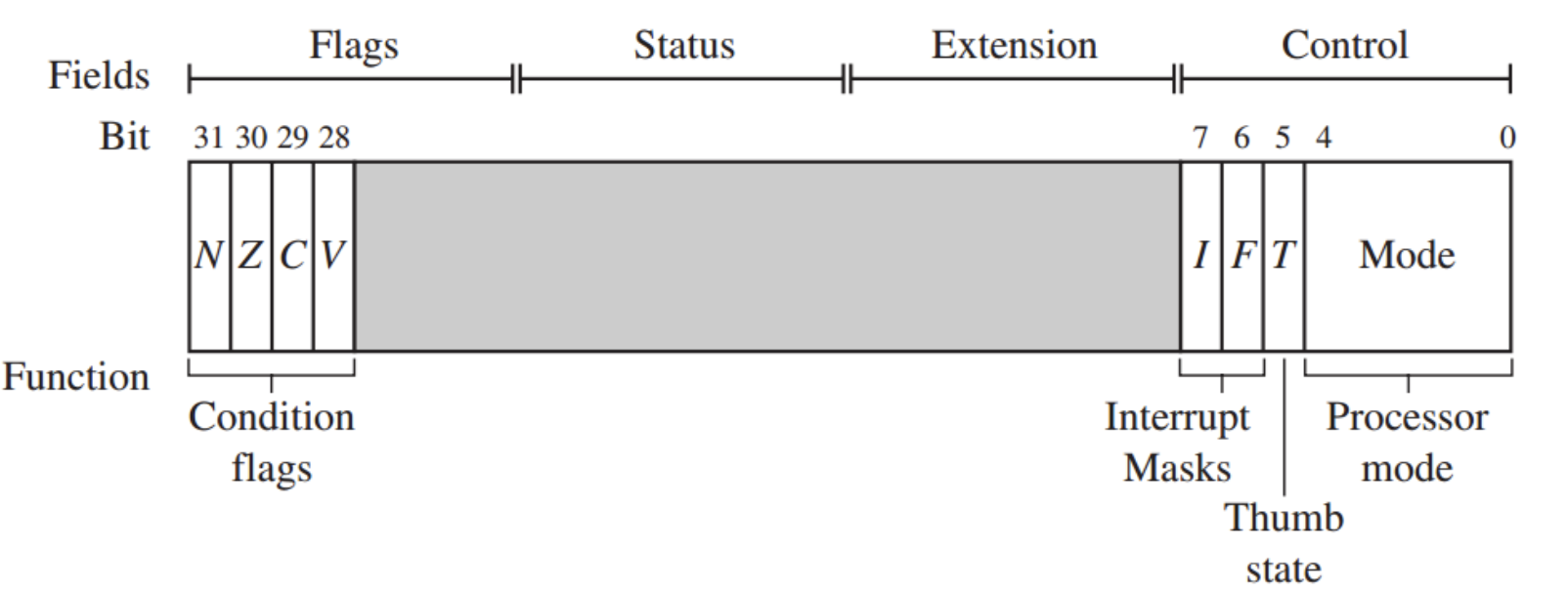

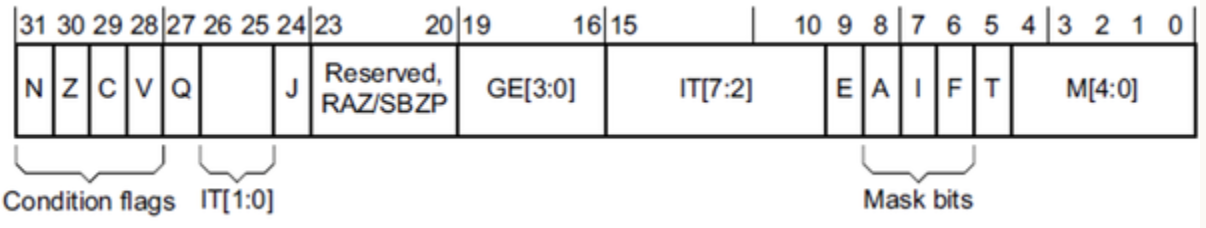

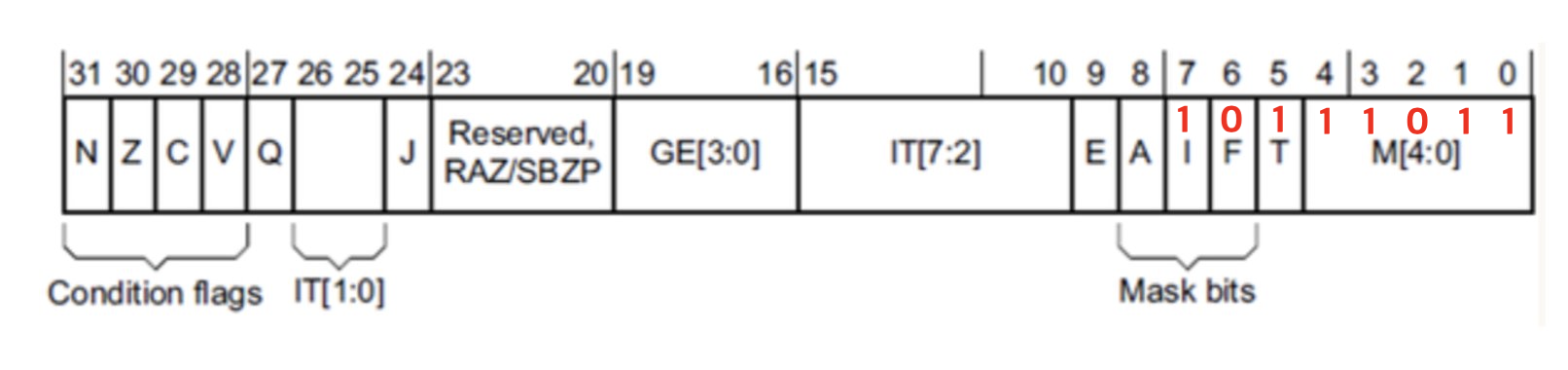

CPSR ( Current Program Status Register )

Figures representing various CPSRs

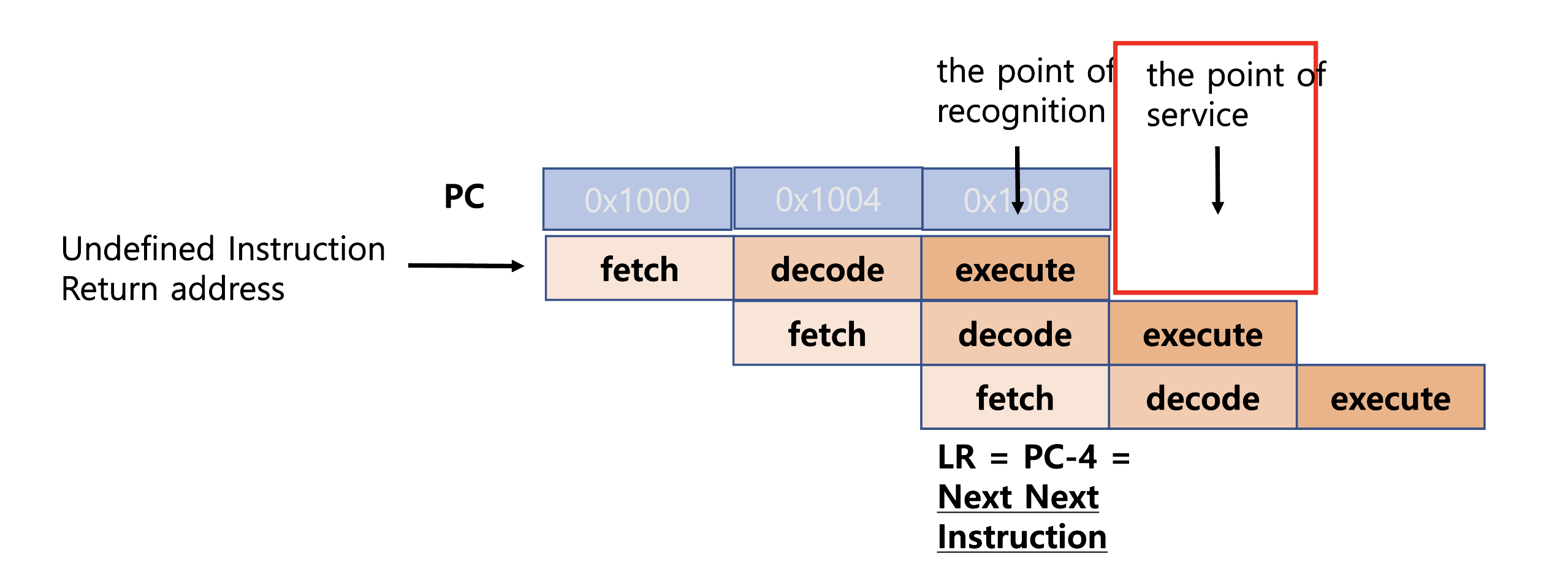

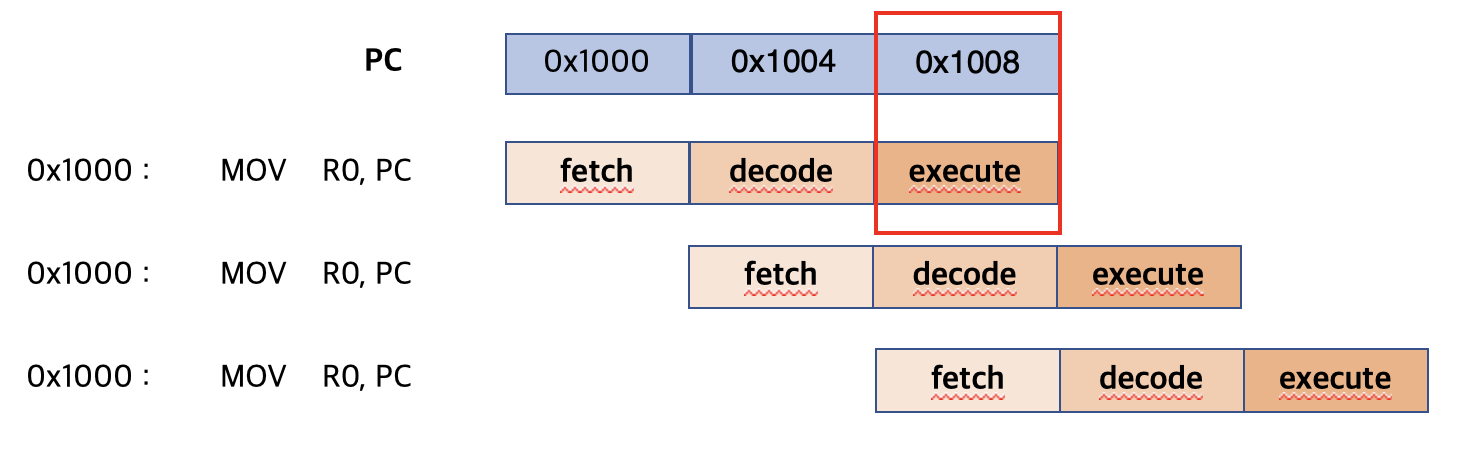

1. Pipleline when PC value changes

When the pc is in the execute stage, the PC contains the next address of the original pc. Therefore, if an exception occurs at the time of the service, the address included in the LR is -4Byte of the current address. Of course, it's a story in ARM mode, and -2Byte in Thumb mode.

2. Exception Process

(1) SPSR_Mode <- CPSR

(2) CPSR change

1) CPSR[5] = 0

2) CPSR[4:0] = Mode

3) CPSR[7] = 1 (Disable IRQ) + CPSR[6] = ? (depends on exception)

(3) LR_Mode <- PC - 4

(4) PC <- corresponding vector address(Exception Vector Base Register + Vector Offset)

(5) Handle excpetion...

(6) CPSR <- SPSR_Mode

(7) PC <- LR

(8) mode change,,

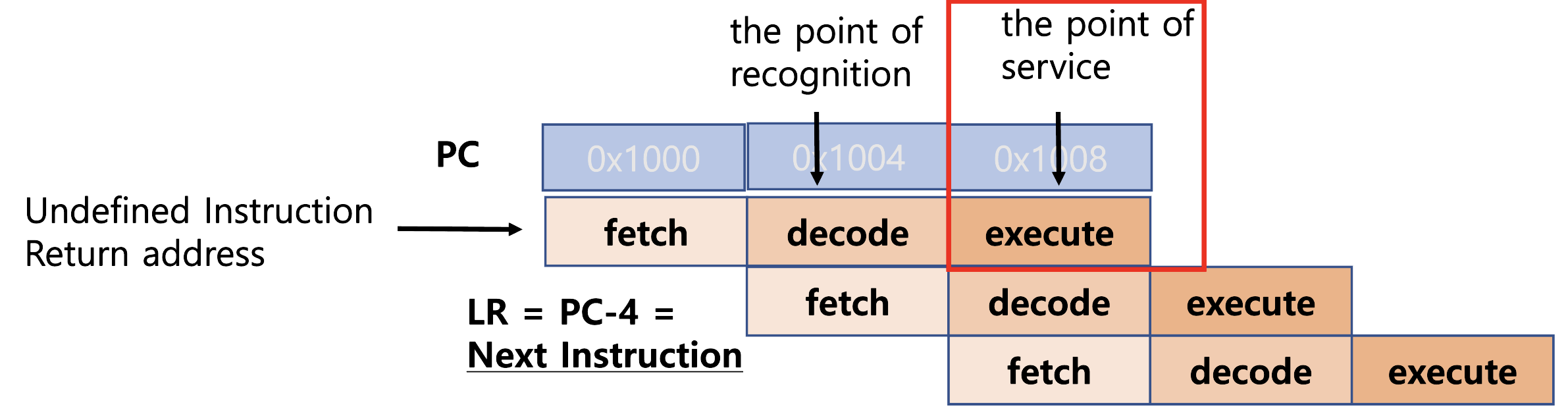

3. Undefined Exception

Cause of occurrence: When a command is determined to be an undefined command when decoding after a command fetch

- For external coprocessor commands, wait for the corresponding coprocessor's ACK.

- Without an ACK, an Undefined exception occurs.

Leverage Exception Handler

- Insert an undefined command at the breakpoint point to use it for debugging purposes

Point of Service and Return Location

Vector Offset would be 0x04.

<LR value>

These are the same in terms of LR being equal to the present value -4 of the PC.

Undefined Exception(Depends on developer wants,,), Supervisor Cell Exception, Prefetch Abort Exception, Secure Monitor Call Exception

VS

4. Data Abort Exception

Cause of occurrence: When loading or storing invalid data memory

* Emergency handling because an Exception occurs at the time the command is executed

Point of service and return location: PC-8 if you want to run it again after fixing the problem.